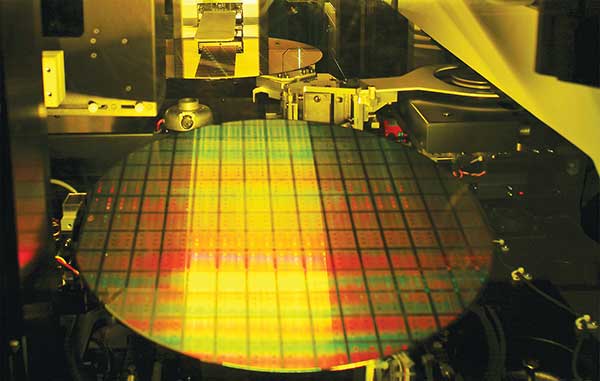

TSMC объявил о завершении работ по разработке инструментов, необходимых для проектирования процессоров, созданных по 5 нм процессу. Компания находится на пути к началу массового производства чипов с использованием этой технологии производства в 2020 году, как предполагалось ранее. Таким образом, тайваньцы получат заметное преимущество перед конкурентами, что с точки зрения возможности сотрудничества с другими структурами чрезвычайно важно для компании.

Следует отметить, что работа над 5 нм технологией уже закончилась некоторое время назад, и последнее объявление относится к инструментам, позволяющим использовать эту литографию. TSMC доработала руководство по проектированию (DRM), подготовила наборы для моделирования процессов и сделала SPICE доступной. Кроме того, клиенты также имеют доступ к полному набору инструментов EDA, предоставляемых Ansys, Cadence, Mentor Graphics и Synopsys. Все эти решения полностью соответствуют требованиям DRM, разработанным тайваньцами, что подтверждается выданными им сертификатами.

Благодаря наличию инструментов, первые производители микросхем уже имеют возможность начать тестовое производство в новом процессе. По данным TSMC, разрабатывается широкий портфель систем, в котором первоначально будут доминировать устройства для рынка высокопроизводительных вычислений и мобильные SoC. Для последнего предприятие также разработало основные ядра для нескольких различных компонентов, включая DDR, LPDDR, PCIe или MIPI. Глядя на спецификацию 5 нм технологии, можно ожидать, что интерес к ее использованию будет довольно большим.

Литография использует как EUV (крайняя ультрафиолетовая литография), так и DUV (глубокая ультрафиолетовая литография) и делает это более эффективно, чем N7 + (7 нм). Например, производитель может применять метод EUV даже для 14 слоев, тогда как в процессе 7 нм FinFET + предел составлял четыре слоя, которые не могли быть ключевыми слоями. По сравнению с 7-нм технологией первого поколения, 5-нм процесс уменьшает размер микросхемы на 45 процентов, увеличивая плотность транзисторов в 1,8 раза. Это позволяет увеличить тактовую частоту на 15 процентов (с тем же энергопотреблением) или уменьшить энергопотребление на 20 процентов (с теми же тактовыми частотами).

— Регулярная проверка качества ссылок по более чем 100 показателям и ежедневный пересчет показателей качества проекта.

— Все известные форматы ссылок: арендные ссылки, вечные ссылки, публикации (упоминания, мнения, отзывы, статьи, пресс-релизы).

— SeoHammer покажет, где рост или падение, а также запросы, на которые нужно обратить внимание.

SeoHammer еще предоставляет технологию Буст, она ускоряет продвижение в десятки раз, а первые результаты появляются уже в течение первых 7 дней. Зарегистрироваться и Начать продвижение